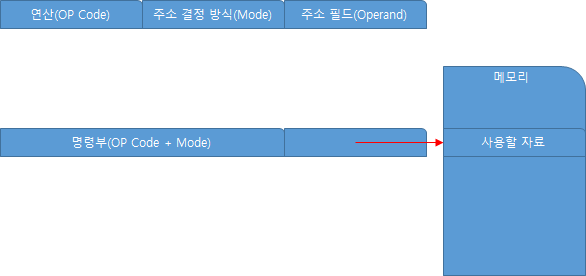

명령어 방식 이번에는 정보처리기사 필기 과목인 전자계산기 구조의 명령어 방식을 알아보아요. 명령어 방식 명령어는 명령부(OP Code + Mode)와 자료부(주소필드, Operand)로 구성합니다. 이 중에 자료부(Operand 부)에 올 수 있는 개수에 따라 명령어 방식을 구분합니다. 0주소 명령어(0 Address Instruction) 1주소 명령어(1 Address Instruction) 2주소 명령어(2 Address Instruction) 3주소 명령어(3 Address Instruction) 0주소 명령어(0 Address Instruction) OP Code 부만 있고 주소를 지정하는 자료부(Operand 부)가 없는 명령어 모든 연산은 Stack 메모리의 TOP(Stack 포인터)이 가리..