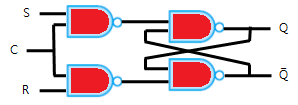

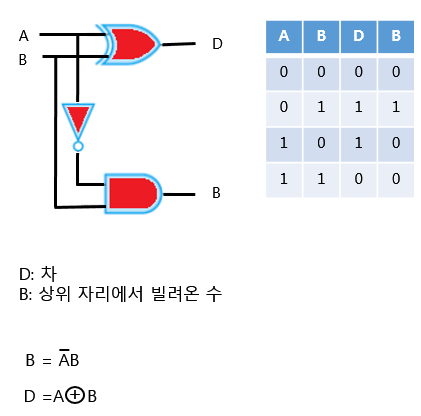

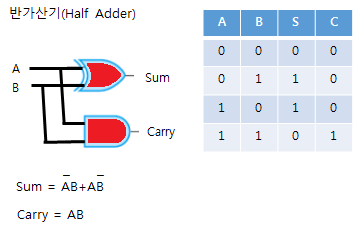

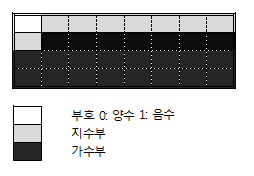

플리플롭 이번에는 정보처리기사 필기 과목인 전자계산기 구조의 플리플롭을 알아보아요. 플리플롭 입력과 클럭(Clock)에 따라 상태가 변하는 순서 논리회로 클럭(Clock) 펄스가 발생하지 않으면 상태가 변하지 않습니다. RS 플리플롭 이전 클락의 값을 유지하거나 0 혹은 1로 설정하는 플립플롭 S은 설정 입력 값이며 R은 리셋 입력 값입니다. S와 R이 0이면 이전 상태를 유지합니다. S와 R을 1로 입력할 수 없습니다. RS 플리플롭 논리회로 RS 플리플롭의 진리표 D 플리플롭 Delay 플리플롭입니다. 입력한 값을 다음 클락의 출력으로 지연하는 플립플롭입니다. RS 플리플롭의 R값을 S의 NOT(인버터)으로 사용하는 플리플롭입니다. D 플리플롭 논리회로 D 플리플롭의 진리표 JK 플리플롭 RS 플리플..