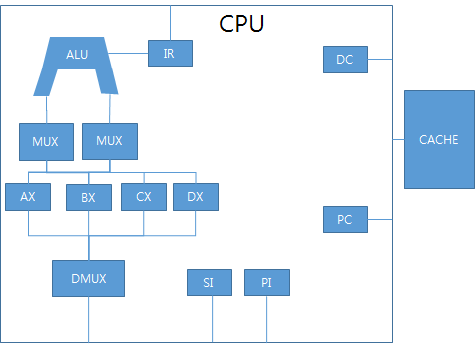

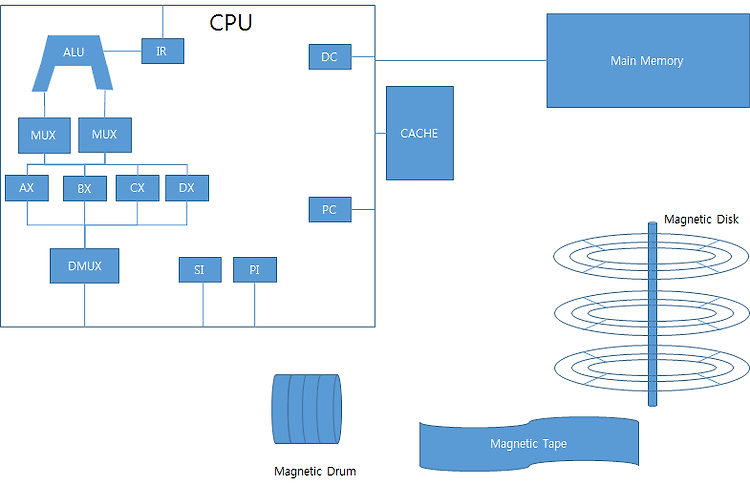

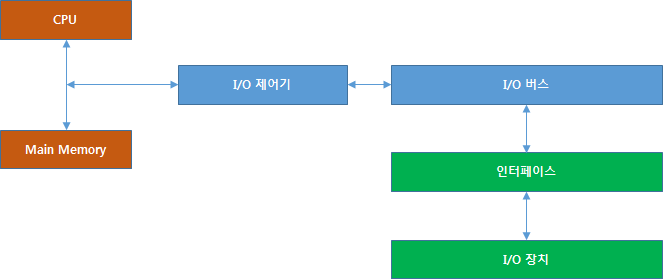

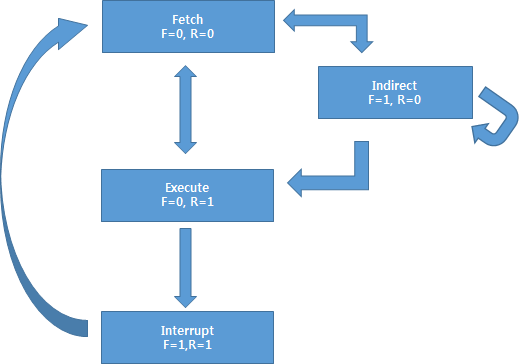

특수 기억장치 이번에는 정보처리기사 필기 과목인 전자계산기 구조의 특수 기억장치를 알아보아요. CPU와 캐시 레지스터 CPU 내부의 계산을 위해 일시적으로 자료나 명령 등을 저장하는 장치로 가장 빠른 기억장치 캐시 메모리 CPU의 처리 속도와 주기억 장치의 속도 차이를 줄이기 위해 사용하는 고속 메모리 버퍼 주기억 장치에 접근 시도를 줄이는 역할을 하여 전체 처리 속도를 향상시킵니다. 적중률 = 적중 횟수/총 접근 횟수 Write Through, Wirte Back, Write Once 쓰기 정책이 있습니다. Write Through: 쓰기 동작을 할 때마다 캐시 메모리와 주기억 장치를 동시에 변경 Write Back: 쓰기 동작 중에는 캐시 내용만 변경하고 캐시에서 제거할 때 주기억 장치에 복사 Wri..